Readings Newsletter

Become a Readings Member to make your shopping experience even easier.

Sign in or sign up for free!

You’re not far away from qualifying for FREE standard shipping within Australia

You’ve qualified for FREE standard shipping within Australia

The cart is loading…

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

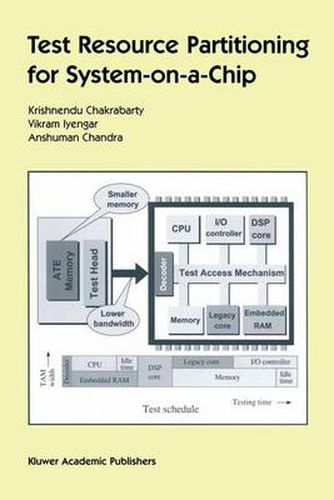

This work explores test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core interfaces as well as core-to-SOC logic interfaces are standardized, such that cores can be easily plugged into virtual sockets on the SOC design, and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator. The goal of the book is to position test resource partitioning in the context of SOC test automation, as well as to generate interest and motivate research on this important topic. SOC integrated circuits composed of embedded cores are commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols. This text responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume. It aims to pave the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

$9.00 standard shipping within Australia

FREE standard shipping within Australia for orders over $100.00

Express & International shipping calculated at checkout

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

This work explores test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core interfaces as well as core-to-SOC logic interfaces are standardized, such that cores can be easily plugged into virtual sockets on the SOC design, and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator. The goal of the book is to position test resource partitioning in the context of SOC test automation, as well as to generate interest and motivate research on this important topic. SOC integrated circuits composed of embedded cores are commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols. This text responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume. It aims to pave the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.