Readings Newsletter

Become a Readings Member to make your shopping experience even easier.

Sign in or sign up for free!

You’re not far away from qualifying for FREE standard shipping within Australia

You’ve qualified for FREE standard shipping within Australia

The cart is loading…

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

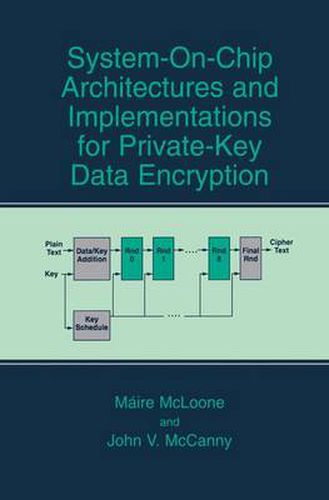

The rapid developments in communication systems have resulted in a need to perform encryption on data in real-time. Encryption of digital information in real-time holds the key to the successful growth of major applications in areas such as satellite communications and electronic commerce. Cryptography is typically a mathematically intensive process which, to date, has mainly been implemented in software. However, such methods are slow and cannot cope with the demands of rapidly growing broadband communication systems. Therefore, innovative hardware solutions involving mapping of complex mathematical operations onto special purpose silicon circuit architectures provide the only feasible solution. In this work, new generic silicon architectures for the DES and Rijndael symmetric key encryption algorithms are presented. The generic architectures can be utilised to rapidly and effortlessly generate system-on-chip cores, which support numerous application requirements, most importantly, different modes of operation and encryption and decryption capabilities. In addition, efficient silicon SHA-1, SHA-2 and HMAC hash algorithm architectures are described. A single-chip Internet Protocol Security (IPSec) architecture is also presented that comprises a generic Rijndael design and a highly efficient HMAC-SHA-1 implementation. In the opinion of the authors, highly efficient hardware implementations of cryptographic algorithms are provided in this book. However, these are not hard-fast solutions. The aim of the book is to provide a guide to the design and development process involved in the translation from encryption algorithm to silicon chip implementation.

$9.00 standard shipping within Australia

FREE standard shipping within Australia for orders over $100.00

Express & International shipping calculated at checkout

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

The rapid developments in communication systems have resulted in a need to perform encryption on data in real-time. Encryption of digital information in real-time holds the key to the successful growth of major applications in areas such as satellite communications and electronic commerce. Cryptography is typically a mathematically intensive process which, to date, has mainly been implemented in software. However, such methods are slow and cannot cope with the demands of rapidly growing broadband communication systems. Therefore, innovative hardware solutions involving mapping of complex mathematical operations onto special purpose silicon circuit architectures provide the only feasible solution. In this work, new generic silicon architectures for the DES and Rijndael symmetric key encryption algorithms are presented. The generic architectures can be utilised to rapidly and effortlessly generate system-on-chip cores, which support numerous application requirements, most importantly, different modes of operation and encryption and decryption capabilities. In addition, efficient silicon SHA-1, SHA-2 and HMAC hash algorithm architectures are described. A single-chip Internet Protocol Security (IPSec) architecture is also presented that comprises a generic Rijndael design and a highly efficient HMAC-SHA-1 implementation. In the opinion of the authors, highly efficient hardware implementations of cryptographic algorithms are provided in this book. However, these are not hard-fast solutions. The aim of the book is to provide a guide to the design and development process involved in the translation from encryption algorithm to silicon chip implementation.